Is Your PCIe 3.0 Receiver Compliant?

Latest News

October 29, 2015

By Tami Pippert, Keysight Technologies, Inc.

PCIe (PCI Express) technology provides a low-cost, scalable point-to-point multi-lane interconnect that has been broadly adopted across numerous applications. Innovations in the PCIe physical layer standards continue to evolve with ever-faster bit rates and increased power management capabilities. As PCIe 3.0 adoption increases, development teams find new challenges in determining physical layer compliance of PCIe 3.0 receivers. Interoperability depends on proper receiver functionality and can only be guaranteed by thorough receiver testing. Mastering the complexity associated with a receiver test bench can be challenging. Becoming familiar with the PCIe 3.0 standard and associated test requirements can help teams prepare.

PCIe 3.0 technology incorporates several changes that enhance its ability to deliver faster rates reliably. The PCIe 3.0 standard enables bit rates up to a whopping 8 GT/s (Giga Transfers per second) while maintaining backwards compatibility with previous PCIe implementations. A device capable of higher data rates must also be compliant at the lower data rates. This means testing at 8 GT/s rates as well as testing at 2.5 GT/s and 5 GT/s. Reducing the 20% 8b/10b version PCIe 2.0 overhead penalty, PCIe 3.0 technology moved to a 128b/130b encoding scheme with scrambling resulting in a mere 1.5% overhead. This makes for faster throughput. For PCIe 3.0 testing, measurement equipment needs to be knowledgeable on PCIe protocol, including encoding and scrambling, not only for the 3.0 standard, but previous standards as well. As PCIe implementations can have different lane widths, each receiver needs to be tested independently as its physical routing and characteristics will differ from other PCIe receivers. Teams will need to understand the implications of setup, configuration and test times associated with testing each lane independently.

PCIe technology has a base spec that defines electrical performance at the device die-pad, while the CEM (Card Electro-Mechanical) spec defines characteristics at the connector. The Base Specification is typically used for ICs (integrated circuits) and has a larger set of tests. The CEM spec is typically used to determine compliance for products that plug into the PCIe connector.

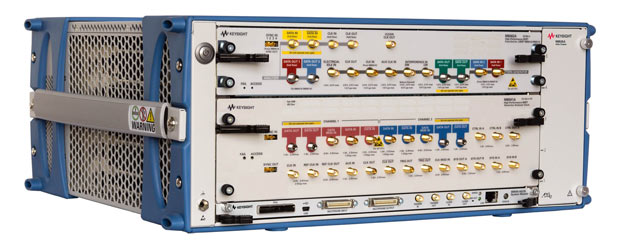

Figure 1. Keysight’s 16.2 Gb/s version of the M8020A J-BERT system is an example of a BERT that can perform receiver testing for all PCIe 3.0 transfer rates. An optional N5990A test automation application automates PCIe 3.0 receiver testing. The J-BERT’s architecture enables it to support current and next-generation receiver validation.

Figure 1. Keysight’s 16.2 Gb/s version of the M8020A J-BERT system is an example of a BERT that can perform receiver testing for all PCIe 3.0 transfer rates. An optional N5990A test automation application automates PCIe 3.0 receiver testing. The J-BERT’s architecture enables it to support current and next-generation receiver validation.Receiver (Rx) testing is used to determine the receiver’s capability to properly detect the digital signal content, even for worst-case impaired input signals. To do this, the transmitter must generate a stress signal. For receiver testing, a BERT (Bit Error Rate Tester) such as the one shown in Fig.1, takes the place of the transmitter. BERT manufacturers offer a PCIe 3.0 application that enables the BERT to be configured to do PCIe 3.0 receiver testing. For example, the application enables the BERT to generate compliance patterns, and produce stress elements that the PCIe 3.0 standard requires for receiver certification. The BERT PCIe 3.0 compliance application also allows automation of test setup and results. This removes the burden of having to understand the specs and how to test from the user. The work was done by the BERT manufacturer who studied the specification and determined how to make each required physical-layer receiver test. BERT manufacturer compliance applications receive certification by the PCI-SIG. BERTs can be configured with multiple technology applications so they can test PCIe 3.0 as well as other high-speed serial standards.

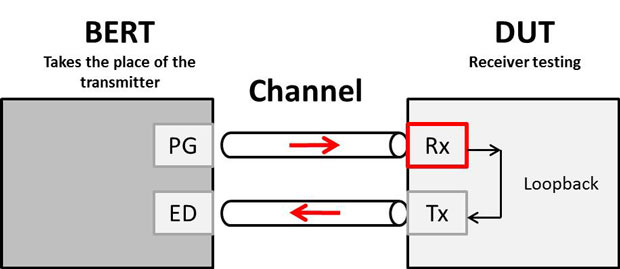

BERTs consists of two key technology blocks, a pattern generator and an error detector. The pattern generator creates the required stress test signal while the error detector determines the bit error rate that the receiver yields under various test conditions. Each of these attributes will be unique to specific standards and are specified by a standards body. As the BERT is taking the place of the transmitter in the link, the BERT needs to have all of the smarts that a transmitter would have when the transmitter/receiver pair perform link training. The BERT applies various compliance test patters at the right time when negotiating with the receiver, and this testing is typically automated with a PCIe 3.0 compliance application that runs on the BERT, see Fig. 2.

Figure 2. For PCIe 3.0 receiver testing the BERT takes the place of the transmitter. The BERT’s pattern generator creates a series of stress signals and the BERT error detector determines how well the receiver tolerates each stress pattern.

Figure 2. For PCIe 3.0 receiver testing the BERT takes the place of the transmitter. The BERT’s pattern generator creates a series of stress signals and the BERT error detector determines how well the receiver tolerates each stress pattern.BERTs need additional capabilities to determine how well the receiver can tolerate additional stress and imperfect signals that wouldn’t ideally be found in a live system. For example, the BERT can apply different types of jitter to determine receiver tolerances. This process can be automated with a PCIe 3.0 compliance application. Calibration of stress test signals requires deep insight into the base specification and measurement techniques, and is another good reason for users to invest in a PCIe 3.0 compliance application for the BERT.

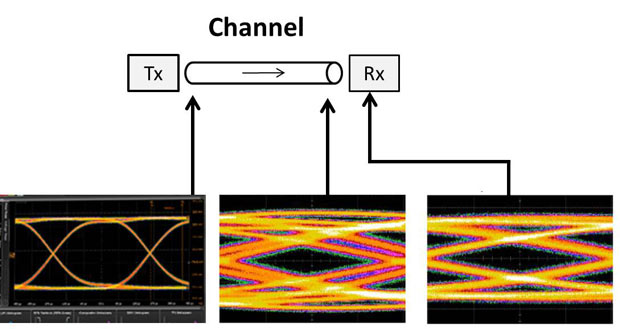

For fast signals, popular FR4 (fire resistant class 4) printed circuit board material attenuates high frequency signals resulting in eyes that are closed at the receiver. PCIe receivers have a BER (bit error ratio) requirement of 10e-12 and at 8 GT/s channel attenuation, closes eyes rendering traditional signals unable to achieve required bit error rates. The receiver can’t determine what the transmitter is sending well enough to ensure the needed reliability. One technology to compensate for this problem in PCIe 3.0 technology is equalization. Equalization compensates for channel insertion loss by boosting higher frequency signal content. De-emphasis, also known as pre-emphasis, is one of the techniques used here. Signals with de-emphasis will have a transition edge and short duration that appears to overshoot the normal resting state of the signal. When a signal changes state from a 1 to a 0, or a 0 to a 1, the transmitter boosts higher frequency signal content. When this modified signal, with the increased high-frequency content, is sent across a channel, the higher frequency content is attenuated. This compensation helps open eyes at the end of the channel. Not only does PCIe 3.0 technology call for equalization at the transmitter, it also incorporates equalization in the receiver as well. For transmitter testing, oscilloscopes have an application that allows them to emulate the receiver’s equalization so that users can see what the signal looks like in the receiver after equalization, see Fig. 3.

Figure 3. PCIe 3.0 technology incorporates both transmitter and receiver equalization. While channel insertion loss would normally cause eyes to be closed at the end of the cable, equalization compensates for the loss and allows the receiver internally to see an open eye.

Figure 3. PCIe 3.0 technology incorporates both transmitter and receiver equalization. While channel insertion loss would normally cause eyes to be closed at the end of the cable, equalization compensates for the loss and allows the receiver internally to see an open eye.PCIe 3.0 technology incorporates link equalization training where the receiver negotiates with the transmitters to apply correct equalization values. For physical-layer compliance, BERTs participate in the negotiation taking the place of the transmitter.

Receiver analysis is critical to PCIe validation and ensuring interoperability of systems. Teams deploying PCIe 3.0 technology should evaluate receiver test options early to determine choices, pricing and how well each solution maps to their needs. Some manufacturers support only receiver testing, only cable testing, or only transmitter testing while others support multiple or all of these. If your company is doing receiver, cable and transmitter testing, it’s often advantageous to work with a vendor who supports and provides equipment, applications and expertise across all of these. The vendor will have thought through the testing implications across all of technical blocks. You’ll also likely have a single point of contact with an application engineer. Ask your manufacture what they support. PCI-SIG is working on development of the 4th generation. BERTs can be expensive, but often have the advantage of working across multiple generations of a technology. Ask your vendor what their plans are for PCIe 4.0 if you plan to move to this generation in the future.

More Info

Subscribe to our FREE magazine, FREE email newsletters or both!

Latest News