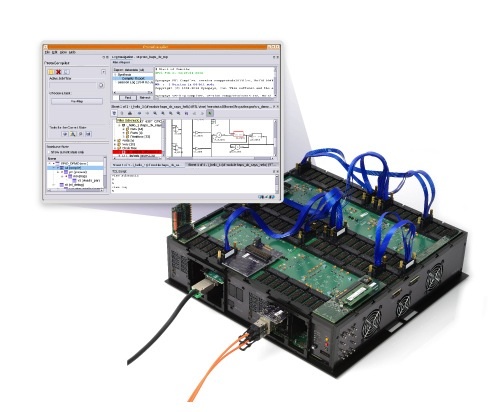

Synopsys’ HAPS-80 Series and ProtoCompiler prototyping solution reduces time to first prototype to under two weeks. Image Courtesy of Synopsys

Latest News

September 16, 2015

Just as product complexity is driving new simulation and prototyping solutions in the mechanical space, the same dynamic is fueling demand for more robust prototyping systems that can facilitate the design and development of on-board chips and related software.

These systems on a chip (SoC) are increasingly becoming a larger piece of the overall product real estate thanks to trends like the Internet of Things (IoT). They require new ways of prototyping that will accelerate the design process, facilitate the integration of hardware and software, and promote system validation of large SoC and GPU (graphics processing unit) designs.

Synopsys’ HAPS-80 Series and ProtoCompiler prototyping solution reduces time to first prototype to under two weeks. Image Courtesy of Synopsys

Synopsys’ HAPS-80 Series and ProtoCompiler prototyping solution reduces time to first prototype to under two weeks. Image Courtesy of SynopsysIn response to this need, Synopsys has introduced HAPS-80, which it calls the first fully-integrated prototyping solution designed to address these rising complexity and time-to-market challenges. The HAPS-80 FPGA-based prototyping system, which includes the ProtoCompiler software, can help reduce the time to first prototype for a SoC to less than two weeks on average, as opposed to the traditional timeframe of about two months, according to Johannes Stahl, Synopsys’ director, product marketing, prototyping.

Workflow Improvements

The HAPS-80 integrated prototyping solution addresses two specific roles as part of the SoC design workflow. The solution allows the development team to design the software in parallel to the chip development, enabling them to run the code on a physical prototype that is a full representation of the entire chip prior to production. In addition, the HAPS-80 solution also facilitates validation, enabling chip designers to visualize complex design behavior in a simulator-like experience, reducing debug time by half, company officials say.

Unlike virtual SoC prototyping solutions used earlier in the electronics design workflow, the HAPS-80 system is a physical platform, combining hardware and software, and is designed to be used in the last three or four months prior to production, when there is a formalized physical representation of a chip, Stahl explains. The platform is also distinguished by its integrated approach, packaging the prototyping capabilities for both hardware and software in a single offering.

“Every one else typically uses separate solutions for hardware and software and tries to bring them together themselves, which can create more work and risks,” Stahl explains. “We are at the point of complexity in prototyping that this separate approach is starting to fail, and our customers pushed us to provide a more integrated solution.”

HAPS-80 also supports designs with up to 1.6 billion ASIC gates, which means it can create a prototype representing the entire chip prior to production, Stahl says. Unlike virtual prototyping solutions that can only be tapped to verify and develop software, a physical prototyping solution like HAPS-80 also ensures that the software will run on the version of the chip that is the most accurate representation of the end product.

While design engineers aren’t the target users for the HAPS-80 platform, they will benefit from its use as part of the larger design workflow, Stahl says. “When you’re prototyping in general, you want to know much earlier in the development cycle that things are going to be correct once you have the final silicon chip in hand and that it will run the right software,” he says.

Check out this video to hear Synopsys execs talk about how the Internet of Things (IoT) will impact product design.

Subscribe to our FREE magazine, FREE email newsletters or both!

Latest News

About the Author

Beth Stackpole is a contributing editor to Digital Engineering. Send e-mail about this article to [email protected].

Follow DE